IEEE 超大規(guī)模集成電路國際研討會(VLSI)和國際電子器件會議(IEDM)是世界學(xué)術(shù)界和企業(yè)界公認(rèn)的半導(dǎo)體器件/工藝領(lǐng)域最高級別會議�,在國際半導(dǎo)體技術(shù)界享有很高的學(xué)術(shù)地位和廣泛的影響力。

2024年6月16至20日,第44屆超大規(guī)模集成電路國際研討會(IEEE Symposium on VLSI Technology and Circuits)在美國夏威夷召開�。華東師大成巖教授研究團隊的最新研究成果以"Polar axis orientation control of hafnium-based ferroelectric capacitors with in-situ AC electric bias during rapid thermal annealing"為題在 VLSI 2024上發(fā)表并作會議報告�。華東師大博士后高兆猛和博士生辛天驕為論文的共同第一作者�����,華東師大成巖教授和中國科學(xué)院微電子研究所呂杭炳研究員為論文的共同通訊作者��。截至目前,極化材料與器件教育部重點實驗室成巖教授研究團隊已有5篇文章發(fā)表于集成電路領(lǐng)域頂會 VLSI 和 IEDM,包括2021年華東師大首篇VLSI和2021年華東師大首篇 IEDM。

華東師大成巖教授研究團隊的最新研究成果在VLSI 2024上發(fā)表并作會議報告

氧化鉿基鐵電隨機存取存儲器(FeRAM)具有非易失、速度快�����、功耗低的優(yōu)點�,在存儲和計算領(lǐng)域中有著極大的應(yīng)用潛力,全球各大半導(dǎo)體企業(yè)和科研機構(gòu)均積極布局研發(fā)。隨著先進制造技術(shù)的不斷發(fā)展和器件單元尺寸的持續(xù)微縮,原子層沉積技術(shù)(ALD)制備的關(guān)鍵存儲介質(zhì)����,即氧化鉿鐵電薄膜具有隨機取向的多晶形態(tài)����,將帶來嚴(yán)重的器件間特性不一致性問題���,阻礙鉿基器件的實用化�。

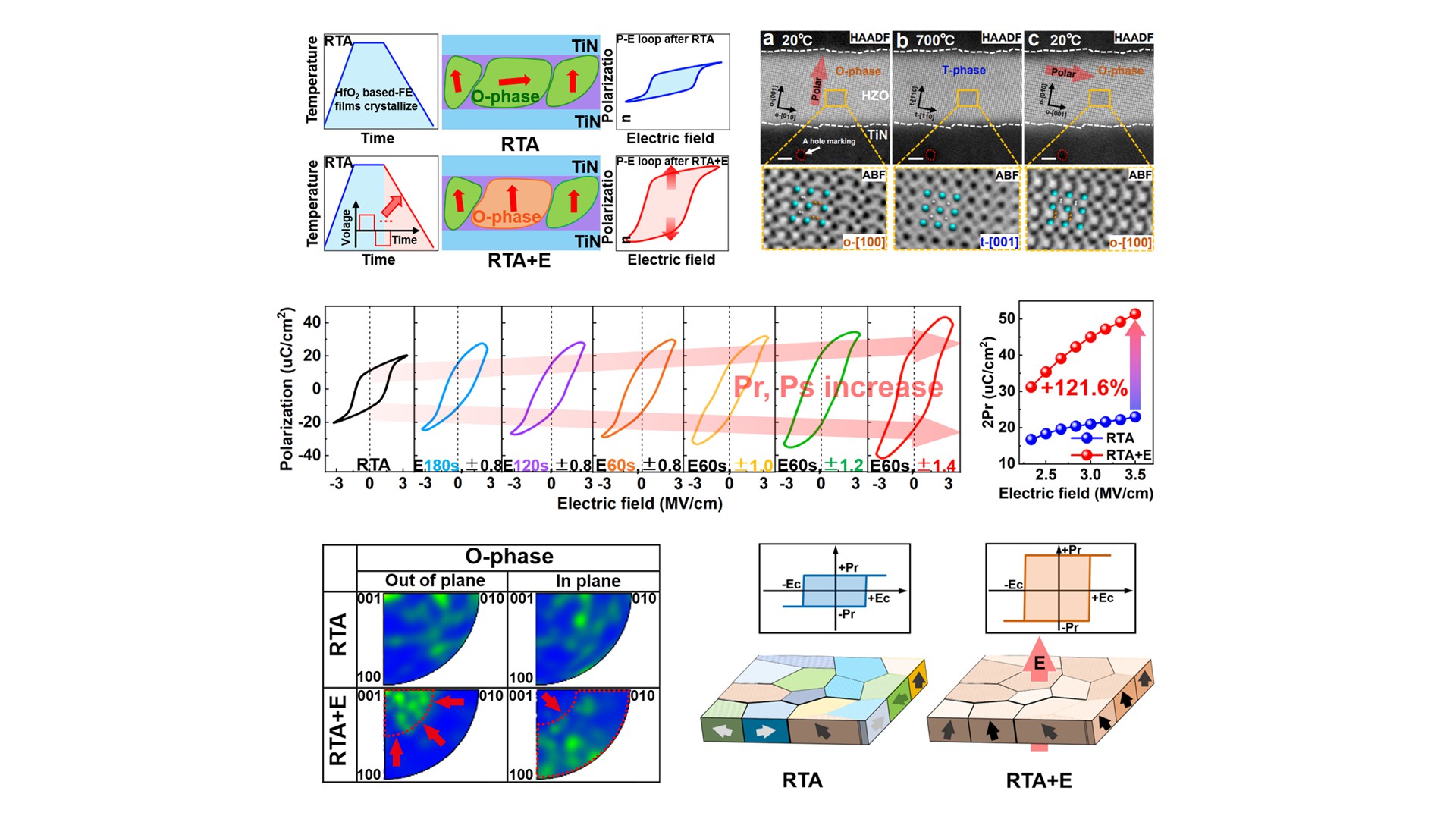

針對上述制約鉿基器件實用化的關(guān)鍵問題�����,團隊聚焦鉿基鐵電電容單元(Fe-CAP)���,深入研究了器件中關(guān)鍵存儲介質(zhì)的微觀結(jié)構(gòu)����,揭示了鐵電相極軸形成源自快速熱退火工藝(RTA)降溫階段的四方→正交相變�。基于上述理論����,團隊創(chuàng)新性地在鉿基 Fe-CAP 的 RTA 工藝中疊加原位交變電場�,達(dá)到了控制鐵電相極軸取向�、并使其趨于一致的目的,獲得了鉿基 Fe-CAP 剩余極化~121.6%的巨大提升�����。進一步,團隊結(jié)合旋進電子衍射(PED)技術(shù)���,統(tǒng)計性地從相結(jié)構(gòu)、極軸取向���、晶粒分布等方面,證實了 RTA 工藝原位疊加交變電場的方法能夠有效控制鐵電相極軸與電場方向趨于一致�����,是器件極化性能提升的主要原因�。上述基于高空間分辨率下的原位外場器件表征技術(shù),從微觀薄膜結(jié)構(gòu)出發(fā)揭示宏觀器件電學(xué)機理,為優(yōu)化器件結(jié)構(gòu)和提升極化性能提供一種有效途徑,為未來鉿基器件的尺寸微縮提供一種解決方案���。

原位交變電場疊加熱工藝實現(xiàn)微觀極軸調(diào)控并獲得宏觀器件極化的極大提升(~121.6%)

VLSI 是超大規(guī)模集成電路和半導(dǎo)體器件領(lǐng)域最頂尖的國際會議之一��,會議研討議題涉及半導(dǎo)體技術(shù)和電路����,匯集了世界各行業(yè)和學(xué)術(shù)界的技術(shù)專家和科學(xué)家����,討論超大規(guī)模集成技術(shù)和電路領(lǐng)域的進展與挑戰(zhàn)。每年 Intel���、Samsung、IBM����、TSMC�����、Micron、SK hynix 等知名半導(dǎo)體公司都在會上發(fā)布最新研究進展��,會議自1980年創(chuàng)辦至今��,44年間在中國大陸地區(qū)共收錄論文112篇����。

附:會議鏈接:https://www.vlsisymposium.org/

來源|物理與電子科學(xué)學(xué)院����、科技處 編輯|鄧安之 編審|郭文君